Synopsys’ FPGA synthesis solution provides Synplify® product to accelerate time-to-shipping hardware with deep debug visibility, incremental design, broad language support, and optimal performance and area for FPGA-based products. FPGAs provide the capabilities that system-on-chip designs require.Accelerate FPGA Design. The following Synplicity tools are available: Synplify Pro Identify. Makes no representations or warranties, either expressed or implied, by or with respect to anything in this manual, and shall not be liable for any implied warranties of merchantability or fitness for aPrograms with an asterisk next to their name are available for download for all. Ii Synplify Pro, May 2000 Related Index Go Back 1st Page Documents Synplify Pro Preface Disclaimer of Warranty Synplicity, Inc.

Synplicity Synplify Pro Down Software Tools From

FPGA vendors are now manufacturing devices at both 130- and 90-nm, half-pitch dimensions. As long as engineers could use only a PLD or an FPGA to implement relatively simple glue-logic circuits, use of ASIC devices that provided greater flexibility and lower volume costs offered the only solution for implementing specific functions on an IC. Synplify also supports the following market requirements:Most FPGA vendors provide their own development-support software.Synplify, Synplify Pro and Synplify Premier are logic synthesis tools provided by Synplicity (Synopsys acquired Synplicity in 2008) specifically for FPGA.Engineers that require the flexibility to target devices from multiple vendors need software tools from traditional EDA vendors.Embedded software and FPGAs: A partnership ready for prime timeAdvances in semiconductor manufacturing are the primary reasons for the increased popularity of FPGAs.

Thus, they allow engineers to use attractive debugging methods, especially in embedded systems, where the integration of hardware and software requires a hardware prototype as early in the development cycle as possible. FPGA devices are attractive, because the cost of modifying an implementation is practically equal to engineering-development cost. The porting is generally easy, because in most applications, engineers do not take advantage of the field programmability of the device, once the major characteristic that differentiated these devices from PLDs. Once volume production shows that a design is stable, engineers can port the design to an ASIC device. A mistake that requires a new set of masks can easily cost $250,000 to $1 million, depending on the severity of the error.Managers are therefore often opting to use FPGA devices, either for the entire life of a product, if applications require only a few tens of thousands of devices, or for prototyping and volume ramp-up. Concurrently, the NRE (nonrecurring-engineering) cost of ASIC devices manufactured with the same 130- and 90-nm technology has risen dramatically.

But the speed required to transfer data and control information among the cores has inspired Nallatech to develop a faster communication approach for FPGAs.System communication can consume as much as 80% of application-development time, according to Craig Sanderson, a system-application engineer at Nallatech. All three popular microprocessor cores—Nios and ARM922T (through a licensing agreement with ARM) from Altera and the PowerPC from Xilinx (through a licensing agreement with IBM)—use standard buses. Of course, cores and proprietary logic blocks must communicate with each other within the device, and engineers until recently implemented this task by using buses. DSP cores and graphics-display cores are becoming available. Designers also need a library of coprocessors and peripheral-IP cores to implement true SOC (system-on-chip) products using FPGA devices (see sidebar “Embedded software and FPGAs: A partnership ready for prime time”).The density and speed of today's offerings from FPGA vendors has convinced IP vendors to port their products to FPGAs. But, beginning with the 130-nm process node, both Altera and Xilinx have provided microprocessor cores, and ARM has also made available many of its standard microprocessor cores in libraries tailored for FPGAs.

At the same time, the difference in device-unit costs between ASICs and FPGAs is becoming smaller. But increasingly, the unit cost of a part during manufacturing is losing significance in the overall product-cost equation, as development costs and costs related to lost market opportunities are escalating by at least one order of magnitude with every new available process technology. Even in large volumes, the cost of one FPGA device is higher than the cost of the same design implemented in ASIC or structured-ASIC technology. Designers can deploy interface nodes at any point within the network as well as insert blocks for communication with external interfaces.The most significant remaining barrier to the widespread use of FPGAs for system design is their unit cost.

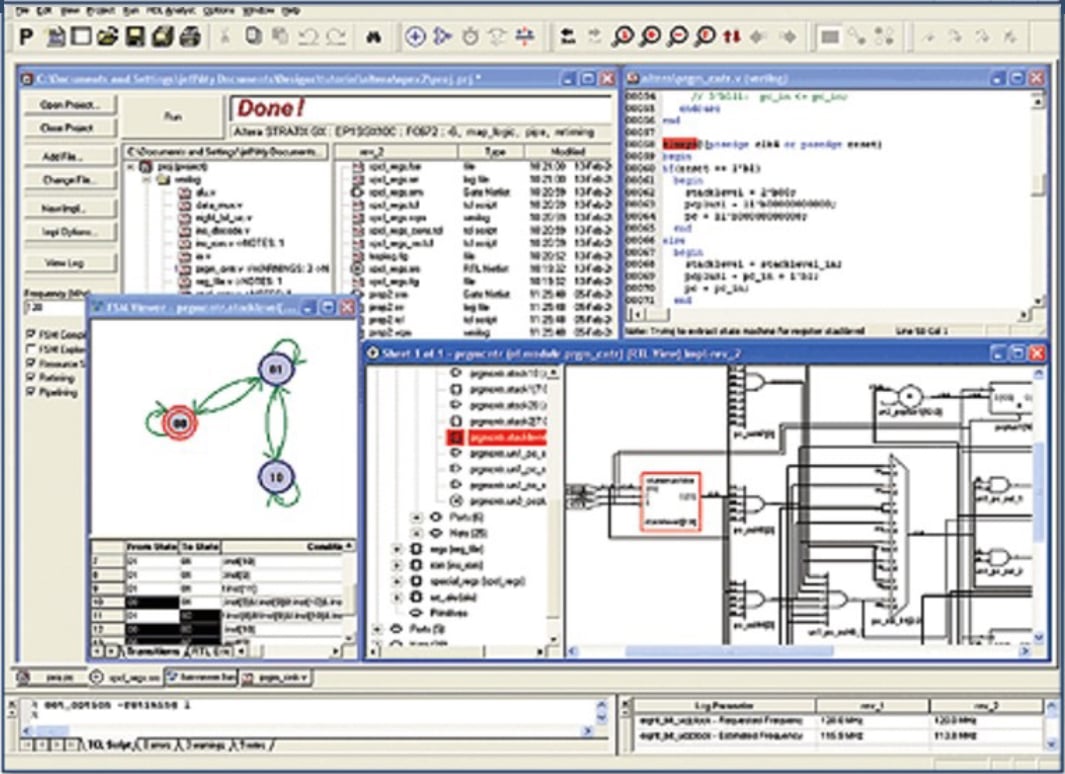

Engineers also receive help during debugging from SignalTap II, an embedded logic-analyzer viewer. The latest version of Quartus II introduces timing- and resource-optimization features to guide users during their design cycles. You can also use tools from both Synplicity and Synopsys in conjunction with the tools available in Quartus II.

The company has recently updated its ISE development environment with version 6.3i, which supports a complete front-to-back flow for FPGA users. List prices for ispLever begin at $995.Xilinx is another FPGA vendor that has invested a considerable amount of money in EDA-tool development designers can choose from five configurations of its ISE design tools. Lattice also provides its own functional simulator. Engineers can choose between synthesis products from Synplicity or Mentor and also receive a version of ModelSim tailored for Lattice-based designs. It includes tools for design entry, project management, design fitting, place and route, floorplanning, device programming, and on-chip logic analysis. It includes all the tools needed to move a programmable-logic design from concept through implementation.

Project Navigator, the main task manager for ISE, lets users configure and drive the design implementation. Engineers can use either ModelSim or Synopsys Verilog simulator with ISE. Xilinx also acquired Hier Design and now offers the RTL floorplanner Plan Ahead as a separate purchasable option for ISE customers.

Vendors either gave free FPGA tools to volume customers or sold them for less than $1000. FPGA vendors developed their own schematic-based tools, because, even today, pc-board designers use schematics to enter designs into the development flow. Most engineers using FPGA and PLD devices were pc-board developers who lacked access to EDA tools targeting IC design. Third-party toolsFor many years, programmable devices were so simple that EDA vendors found that they could not charge enough for the tools to justify entering the market. The five configurations of ISE range in price from a free Web-downloadable package to ISE Foundation for $2495.

0 kommentar(er)

0 kommentar(er)